Hello! I'm Parsa Mirfasihi

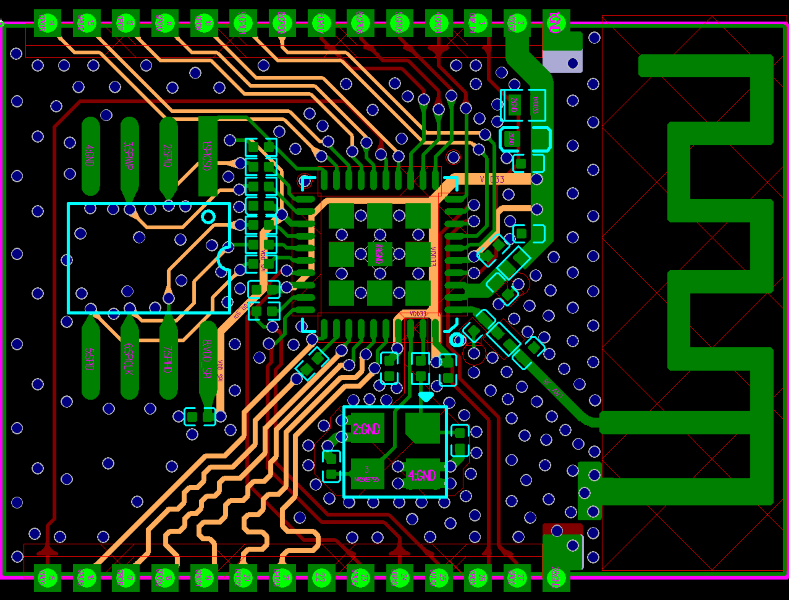

As a passionate VLSI and hardware design enthusiast, I specialize in developing efficient and high-performance hardware solutions with a strong focus on innovation and reliability. My expertise spans the complete ASIC workflow and RTL-to-GDSII flow, including physical design, digital design verification, FPGA-based system design, low-power optimization, SRAM circuit design, and static timing analysis. Proficient in industry-standard Synopsys and Cadence tools, I excel at optimizing circuits for speed, power, and area while ensuring robust hardware security. In addition to my hardware expertise, I leverage Python to develop automation scripts and verification frameworks, enhancing design validation and streamlining workflows. With strong proficiency in SystemVerilog and advanced verification methodologies, I continuously push the boundaries of next-generation semiconductor technologies and hardware optimization.